�l���r�g�����ٷ��Ӌ��C�QՓ���g�[��1��

ժ Ҫ�� ժ Ҫ�������о� H D B3 �a�ľ��aԭ���������˃ɷN�����팍�F H D B3 �a���a��������һ�����M�з� 0 �a�ĘO��׃�������O�ԵIJ� V ������Ȼ�����M�Ў��O�Բ� B ����;�����������M�в� V ���������M�в� B ������������M�ИO��׃���������C�ɵã����r��l�ʞ� 100 M H

����ժ Ҫ�������о� H D B3 �a�ľ��aԭ���������˃ɷN�����팍�F H D B3 �a���a��������һ�����M�з� 0 �a�ĘO��׃�������O�ԵIJ� V ������Ȼ�����M�Ў��O�Բ� B ����;�����������M�в� V ���������M�в� B ������������M�ИO��׃���������C�ɵã����r��l�ʞ� 100 M H z�r���mȻ�ɷN�������܌��F H D B3 �a�ľ��a�����ҹ�����ͬ�����ǃɷN����Ӳ���·��ռ�õĿ�߉��Ԫ����ͬ��������ռ�õĿ�߉��Ԫ�ȷ���һ�� 9 ������ˣ��ڹ���һ������r�£����������ڷ���һ��

�����P�I�~��FPG A ;H D B3 �a;߉�YԴ;����

���������m���ŵ�����̖�ڂ�ݔǰһ��Ҫ�M�о��a̎��[1]�����a��ʽ��N���ӣ��� H D B3 �a���l�ɷ��٣��B�m�� 0 �����^ 3 �������ҟoֱ�����ԣ����ԑ��÷����^�V[2]�����о����� V H D L �Z�ԣ��OӋ�˃ɷN H D B3 �a���a���������@�ɷN���aϵ�y�M���ˌ��ȷ���[3]��

����1���a���aԭ��

����H D B3 �a��Ҫ�� 3 ���P�I���E�@�ã����ИO��׃�������в� V ���������в� B ����[4]��

�������ИO��׃�����z�y���� 0 �a�r������O��������ؓ׃��[5 6]��

�������в� V ���������������z�y���B�m 4 �� 0���t��ԓ̎���� V ��������rԭ��ݔ����

�������в� B �������Д�ݔ�������Ѓɂ����� V ��̖֮�g�ķ� 0 �a�����������ֵ��ż������ô�㌢ B �a���������Ќ�����λ�ã���t�ͱ���ԭ��ݔ����

�������OӋ�У��ɷN������ 3 ���P�I���E�������һ�ӡ�����һ���Ȍ������M�з� 0 �a�O��׃�������O�Բ� V ������Ȼ���ٌ������M�Ў��O�Բ� B ����;�����������M�в� V ������Ȼ�����M�в� B ������������M�ИO��׃����

����2���a��Ӳ���·

����2.1 ����һ��Ӳ���·

����chaV �Ƿ� 0 �a�O���γɼ����O�Բ� V ģ�K���ڴ�Ӳ���·�У�ԓ����ģ�K�� flag_v_1�vflag_v_v�w����ǰ һ���� 0 �a�vǰһ V �a�w�ĘO�ԣ�����־��̖�� 0 �t����O�Ԟ�ؓ������ 1 �t����[7]����ݔ����̖ input�� 1 �r������ flag_v_1 ��ֵ��out_v ݔ�������ĘO����̖[8];��ݔ����̖ input�� 0 �r����ô����Ӌ�������M�м�һ�������c��ͬ�r�Д�ԓӋ������ֵ�Ƿ���� 4��������õ��� 4����ô out_v �˿ڱ�ݔ��һ�� V�v�ׂ� V ����̖ؓ�cǰһ���� 0 ��̖������ͬ������ V �ķ�̖��ؓ׃���w����tԭ��ݔ��[9]��

����chaB �ǎ��O�ԵIJ� B ģ�K���ڴ�Ӳ���·�У�ԓ����ģ�K������λ��λ�Ĵ������M�Ў��O�Բ� B �������� chaV ģ�K��ݔ����̖ out_v ݔ����λ�Ĵ����r��chaB ģ�K�е���λ�Ĵ����ĵ��ļ�ͬ�r�Д�ԓݔ����̖�Ƿ�� V�v+ V �� V�w������ǣ����^�m�Дஔǰ V �ĘO���Ƿ��ǰһ���� 0 �a�O����ͬ�������ͬ����ô out_b ��ԭ��ݔ�����������ͬ����ô out_b ��ݔ���c��ǰ V �O����ͬ�� B�v���ڲ�������λ�Ĵ�����ʹ�����ݔ���� B �ڃɂ� V �a֮�g��һ���� 0 ��̖��w��

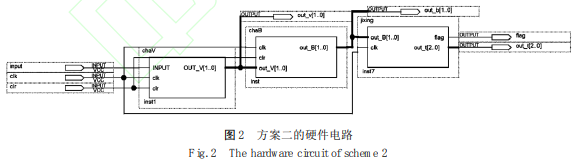

����2.2 ��������Ӳ���·

������������Ӳ���·��D 2 ��ʾ��chaV ��chaB��jixing �քe�Dz� V ģ�K���� B ģ�K�͘O���γ�ģ�K��

�����ڴ�Ӳ���·�У�chaV ģ�K���Д�ݔ����̖ input�Ƿ�� 0�����ǣ��t�^�m�Д��Ƿ��� 4 �� 0�����ǣ��t�� out_v ݔ�� V�v�����O�ԩw��������rԭ��ݔ����chaB ģ�K������λ��λ�Ĵ������M�в����O�Բ� B �������� chaV ģ�Kݔ������̖ out_v ݔ����λ�Ĵ����r��chaB ģ�K�е���λ�Ĵ����ĵ� 4 ��ͬ�r�Д�ԓݔ����̖�Ƿ�� V ������ V ���t�_ʼӋ���� 0 �a�Ă�����ֱ����һ�� V �Y��Ӌ����ͬ�r�Д�ԓӋ��ֵ����ż�ԣ�����ż�����tݔ�� B�v���� chaB ģ�K��������λ�Ĵ�����ʹ����Kݔ���� B �� 2 �� V �a�к�һ�� 0 ��̖��w����tԭ��ݔ����

������ out_b ��̖�M�� jixing ģ�K�r��ԓģ�K���� flag ��̖�vǰһ�� 0 �a�c B �ĘO�Ԙ�־�w�� 0 �� B �M����ؓ�O�Խ��棬ͬ�rҲ�ɵõ� V �ĘO�ԣ���ݔ�� H D B3 �a out_t��

����3������Y��������

����3.1 ����һ�ķ���Y���c����

�����ڴ˷����У�input��ݔ��Ĵ����a��̖��clk �� 100 M H z�r状ˣ�clr������ˣ�flag_v_1��flag_v_v �քe��ǰһ�� 0 �a��ǰһ V �a�ĘO�Ԙ�־���ɷ���ɵã���ݔ�� 10011000011100001100001011 �r���� V �������O���γ���̖ out_v �� + 100 1 + 1000 + V 1 + 1 1000 V + 1 1000 + V 10 + 1 1�v����� 0 ���� 0��1 ���� B��2 �� �� 1��3 �� �� V ��5 �� �� + B��6 �� �� + 1��7 �� �� + V ���� ô �� �� �� ʮ �M �� �� 60026000726200036200072062�w���� B �����̖�vH D B3 �a���a��̖�wout_b �� + 100 1 + 1000 + V 1 + 11000 V + 1 1 + B00 + V 1 + 1 1�v������ʮ�M�ƞ� 60026000726200036250072062�w��������ʹ������λ�Ĵ���������ݔ�������t[10]��

��������һ�Ĺ�����D 4 ��ʾ�������Ğ� 63.86 m W ���o�B���Ğ� 60.15 m W ��I/O ���Ğ� 3.71 m W ��

��������һ���YԴռ����D 5 ��ʾ���M��߉ռ�� 57 ����߉��Ԫ��ռ�� 69 ����

����3.2 �������ķ���Y���c����

�����������ķ���Y����D 6 ��ʾ

����10011000V 111000V 11000V 1011�v���� 0 �� �� 0��1 �� �� 1��2 �� �� B��3 �� �� V ���� ô �� �� �� ʮ �M �� �� 10011000311100031100031011�w���� B ���������̖ out_b �� 0011000V 111000V 11B00V 1011�v0 ���� 0��1 ���� 1��2 ���� B��3 ���� V ����ô������ʮ�M�ƞ� 10011000311100031120031011 �w���O���D�������̖�vH D B3 �a���a��̖�wout_t�� + 100 1 + 1000 + V 1 + 1 1000 V + 1 1 + B00 + V 10 + 1 1�v0 ���� 0��1 ���� B��2 �� �� 1��3 �� �� V ��5 �� �� + B��6 �� �� + 1��7 �� �� + V ���� ô �� �� �� ʮ �M �� �� 60026000726200036250072062�w��������ʹ������λ�Ĵ���������ݔ�������t��

�����������Ĺ�����D 7 ��ʾ�������Ğ� 63.86 m W ���o�B���Ğ� 60.15 m W ��I/O ���Ğ� 3.71 m W ��

����4�����ȷ���

�������OӋ�У��ɷN������ 3 ���P�I���E�������һ�ӣ�����һ�����M�з� 0 �a�O��׃�������O�Բ� V ������Ȼ�����M�Ў��O�Բ� B ����;�����������M�в� V ������Ȼ���M�в� B ������������M�ИO��׃�����mȻ�����ɷN�������܌�ݔ����̖�M�� H D B3 �a���a�����ҹ�����ͬ������ռ�õ�߉�YԴ��ͬ�����ܱ��^��� 1 ��ʾ��

�����ı� 1 ���Կ������ڹ�����ͬ����r�£�������ռ�õĿ�߉��Ԫ�ȷ���һ�� 9 ���������������f���������ڷ���һ���������OӋ���ܲ�����ģ��Y��߀�����`������ں��m�Ĺ�������Ҫ�^�m�����@�ɷN������——Փ�����ߣ��� �N��Ф���

���������īI��

����[1] �μ������S�ǂ�.����ͨ��ϵ�y��ģ�c�OӋ[M ].��������ӹ��I�����磬2004��1 288.

����[2] �����ţ������dzɿ�.ͨ��ԭ��[M ].5 ��.�������������I�����磬2001��77 78.

����[3] ���.���� FPG A �� LD PC �a�g�a���о�[D ].�B�T���A�S��W��2018.

����[4] ������.���� CPLD �� H D B3 �a����a�·���OӋ[J].Ӌ��C��Ϣ��2010��26�v2�w��169 171.

����[5] �x�ĝ�.���� SO PC ���g�� H D B3 ���a���OӋ[D ].�������L����W��2014.

����[6] ���.���� System V iew �� H D B3 ���a���OӋ[J].��Ϣͨ�ţ�2014�v9�w��41.

����[7] ��־�������d������.���� FPG A �� H D B3 ����a�������������늌�̽����Ӝy���еđ���[J].ʯ�̓x���� 2012��26�v2�w��76 79.

����[8] �̱�.���A���ܶ��p�O�� H D B3 �a����a�� V H D L �OӋ������[D ].�K�ݣ��K�ݴ�W��2008.

����[9] ����������̩.���� FPG A �� H D B3 �a���a�������OӋ�c����[J].�F����Ӽ��g��2011��34�v24�w��146 148.

����[10] ���ɣ��S�^�I.ED A ���ý̳�[M ].�������ƌW�����磬2005��77 79.